Триггеры (RS, D, JK, T- типов): принцип работы, функциональная схема, временная диаграмма, параметры, примеры использования, микросхемное исполнение

Триггер - это запоминающее устройство, хранящее одно из двух состояний - либо 0 либо 1.

Содержание

Является синхронным триггером

Таким образом триггер сохраняет значение поданное на вход D.

Рис. 14. Условное обозначение D-триггера, его реализация и временные диаграммы его работы.

Рис. 15. Временные диаграммы.

При C=0 и R=S=1 возникает запрещенное состояние.

Предназначен для хранения информации на входе D при C=1

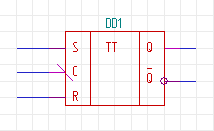

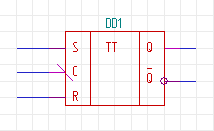

Рис. 16. Условное обозначение T-триггера.

Триггер при подаче сигнала синхронизации меняет значение на выходе на противоположное. Может иметь вход стробирования Е (при Е=0 триггер не изменяет значение на выходе ни при каких условиях).

Рис. 17. Схема T-триггера.

Если импульс синхронизации короткий (менее времени переключения триггера) то триггер работает в штатном режиме. При длительном импульсе синхронизации возможен автоколебательный режим.

Может быть реализован и на синхронном RS-триггере (рис. 5.3).

Рис. 18. Реализация T-триггера на базе RS-триггера.

Короткие импульсы синхронизации (менее времени срабатывания триггера) не совсем удобны для управления триггерами. Как вариант модернизации существуют двухступенчатые триггеры. Они реагируют на смену значения на входе синхронизации (фронт:0-1, либо спад:1-0).

В основе - RS триггер.

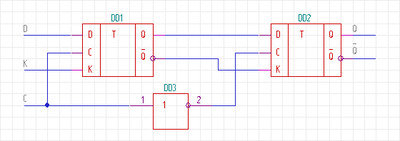

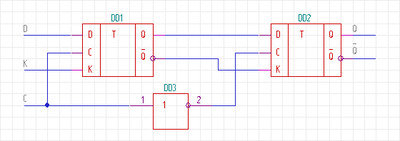

Рис. 19. Общий вид двухступенчатых триггеров.

Перезапись из первой во вторую ступень происходит при смене значения входа синхронизации.

Рис. 20. Схема двухступенчатого синхронного RS-триггера.

Запись происходит по спаду (изменение с 1 до 0). Основа - два обычных RS-триггера. Запись в первый триггер происходит при С=1 (второй триггер в это время в режиме хранения). При смене значения С на С=0 происходит запись значений из первого триггера во второй. Таким образом запись происходит по спаду сигнала синхронизации С (это обозначается наклонной чертой на входе синхронизации в обозначении триггера на схеме - см. рис 6.3).

Рис. 21. Условное обозначение двухступенчатого синхронного RS-триггера.

Рис. 22. Схема и условное обозначение двухступенчатого D-триггера.

Логика работы та же что и у RS-триггера. С=1 - запись в первый триггер, С=0 - запись из первого во второй (запись по спаду).

Рис. 23. Схема двухступенчатого JK-триггера.

Поведение аналогично предыдущим триггерам кроме состояния J=1 K=1. Рассмотрим это состояние. При J=1K=1 и C=1 возникает автоколебательный процесс: 0, 1, 0, 1 и т.д. JK-триггер должен переключаться в состояние, противоположное тому, в котором находится 2-й триггер, т.е. используются только внутренние обратные связи (ОС).

Для устранения этого недостатка можно модифицировать схему (рис. 24)

Рис. 24. Схема двухступенчатого JK-триггера (без автоколебательного процесса).

Особенность схемы - наличие глубокой обратной связи (а именно, связи выходов второй ступени со входами первой ступени). В результате в триггер первой ступени записываются только значения. противоположные значениям на выходе, поэтому нет колебательного процесса (и генерации случайных чисел заодно).

Двухступенчатые триггеры изменяют свои значения по спаду/фронту синхроимпульса, поэтому длительность импульсов не важна.

Приведенные выше (рис. 23 и 24) схемы являются базовыми, теперь следует рассмотреть конкретные реализации.

Рис. 25. Реализация двухступенчатого JK-триггера на базе элементов "И-НЕ".

На входы D1 и D2 идет обратная связь с выходов D7, D8. Запись происходит при условии, что на выходах D1 и D2 одновременно присутствуют "1" (запись во вторую ступень). Запись в первую ступень происходит при противоположных значениях на выходах D7, D8. Запись в первую ступень происходит либо при C=1, либо при J=K=0. Перезапись - при C=0 (на выходах D1 и D2 - единицы).

Еще эту схему можно получить на базе RS-триггеров (вывод схемы - на рис. 26)

Рис. 26. Реализация двухступенчатого JK-триггера на основе RS-триггера (вывод схемы).

Рис. 27. Пример универсального триггера.

При необходимости в схему можно ввести асинхронные входы установки в 0 и 1 - они устанавливают схему независимо от схемы управления. Триггер сч такими входами называется универсальным (т.е. он имеет и синхронные. и асинхронные входы установки). Асинхронные входы нужны для инициализации. Пример - рис 27, вход Reset переустановка всех компонентов схемы в начальное состояние. В режиме хранения требуется реагирование на синхронные входы (на их значения). При режиме записи - приоритет у асинхронных входов.

Рис. 28. Обозначение универсального JK-триггера.

Имеет как синхронные, так и асинхронные входы установки. Конъюнкции D1 и D2 могут быть и 3х-входовыми, и 6-тивходовыми, а могут иметь и большую размерность, следовательно, вместо одного сигнала J приходят несколько сигналов, объединенных конъюнкциями. Другими словами, на входе появляется "1", если на всех J - "1". Для входа K ситуация аналогичная.

Классическая схема ступенчатого D-триггера представлена на рисунке 29.

Рис. 29. Разработка ступенчатого D-триггера.

Состоит из трех асинхронных RS-триггеров (состоят из D1-D2, D3-D4, D5-D6 соответственно). Первую ступень образуют два триггера: (D1-D2) и (D3-D4), а вторая образуется, соответственно, на базе *D5-D6).

Первую ступень образуют два триггера: (D1-D2) и (D3-D4), а вторая образуется, соответственно, на базе *D5-D6).

T3 - с инверсными входами (рем хранение - оба значения равны "1"). Если C=0, то T2=T3=1, то есть при C=0T3=1, а при C=1 T3 определяется тем, что подается на вход D.

При C=0,D=0 в T1 записывается некоторое значение, а T2 находится в запрещенном состоянии (две "1").

Если при C=1 T2=1 и T3=0, то произойдет переход в режим записи и произойдет запись "0" во вторую ступень.

Рассмотрим случай, когда C=0,D=1. Пусть D4=0, вход D4=0, тогда D1=1, можно наблюдать противоположную картину: T2 находится в режиме записи значения, а T1 - в запрещенном состоянии.

Рис. 8.2. Условное обозначение ступенчатого D-триггера.

При переключении C из "0" в "1" на D3 происходит то же изменение, что и на D2 - переход из 1 в 0. Тогда T3 находится в режиме записи логической единицы:

(0)Q→1

(1)¯Q→0

При C=1 значение на входе D поменяется: 1→0, выход D4 установится в значение логической "1", поэтому D1 станет равным 1 (его значение на выходе не меняется, на D2 - то же самое (только там - логический 0), поэтому значение на выходе D3 не меняется за счет D1 и D2).

При C=1 значение на входе D изменяется в порядке 1→0→1, значение D3 меняться не будет. Следовательно, при C=0 на выходе значение не будет меняться, при C=1 значение на выходе тоже не меняется. Таким образом, запись производится при переключении с 0 на 1 (по фронту).

- Первый триггер - для фиксации того, что хотим записать "0";

- Второй триггер - для фиксации того, что хотим записать "1".

В итоге, при C:0→1 происходит запись, то есть переключение в другое состояние (или в запрещенное состояние).

Рис. 30. Условное обозначение ступенчатого D-триггера.

Рис. 31. Преобразование ступенчатого D-триггера в универсальный.

Рис. 32. Условное графическое обозначение универсального D-триггера.