Оперативные запоминающие устройства

Содержание

Статические ОЗУ

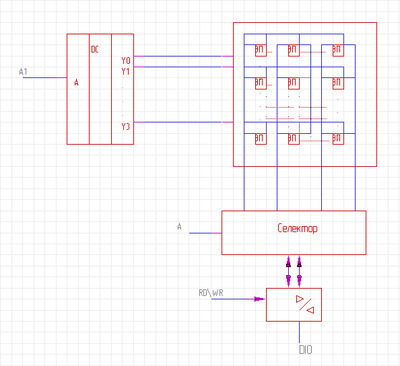

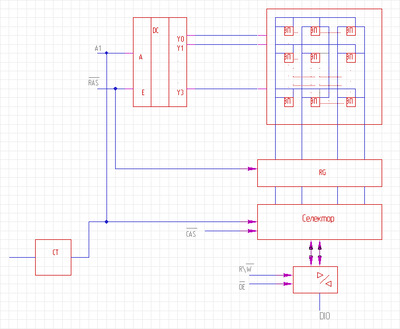

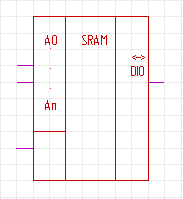

Рис 1.1 Статическое ОЗУ. Общая схема

Элемент памяти статической ОЗУ - триггер.

Селектор выбирает в выбранной строке элемент памяти (ЭП) (к нему подходят 2 двунаправленные шины), далее подсоединяется буфер.

Вместо одной шины - две, при этом они используются для чтения/записи информации в ЭП.

Селектор двунаправленный (от матрицы ЭП - устройству, так и от устройства - матрице ЭП).

Устройство буфер чтения/записи содержит усилитель сигнала (т.е. используется развязка схем)

Может быть как 1 двунаправленный выход, так и 2 однонаправленных выхода.

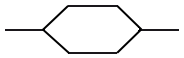

Условное обозначение

Сигналы WR/RD могут быть и раздельными (когда ни один из сигналов не импульс)

Рис 1.2 Условное обозначение

ЭП статического ОЗУ для КМОП логики

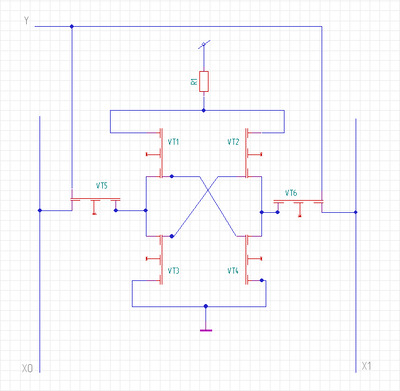

Рис 1.3 Элемент памяти статического ОЗУ для КМОП логики

Основа - RS-триггер

VT1, VT2, VT3, VT4 - RS-триггер.

VT5, VT6 - коммутация (триггерные ключи).

Y - шина для выбора ЭП.

A, B - прямой и инверсный входы и выходы триггера соответственно.

X0, X1 - шины данных.

Считается, когда активна одна из шин:

- "0" (X0)

- "1" (X1)

Когда транзистор в "0":

- VT1, VT4 - открыты

- VT2, VT3 - закрыты

Когда транзистор в "1":

- VT2, VT3 - открыты

- VT1, VT4 - закрыты

При "1" на Y: Открыты VT5, VT6. A,B подключены к X0, X1 соответственно (режим чтения, записи информации).

При "0" на Y: Отключены VT1, VT4 (режим хранения).

Состояния триггера: "0": A = Eпит, т.к. VT1 - открыт, VT3 - закрыт, т.к. узел A не связан с затвором VT1 VT2, VT3 - потенциал земли, B = 0.

"1": B = Eпит.

A = "0".

Если триггер в "0", а X0 = "1", X1 = "0".

Если X1 = "1", X0 = "0", то происходит переброс триггера в противоположное состояние. Для избежания высокого тока в цепь питания ставят токоограничивающий резистор (проходит только с МОП-транзисторами).

Шины X0, X1 двунаправленные ("0", "1" подают на них в зависимости от требуемого состояния).

Запись: подаём на X0, X1 разные потенциалы. После записи значение сохраняется (поддерживается потенциал).

Загруженное состояние:

X0 = "0", X1 = "0"

или

X0 = "1", X1 = "1".

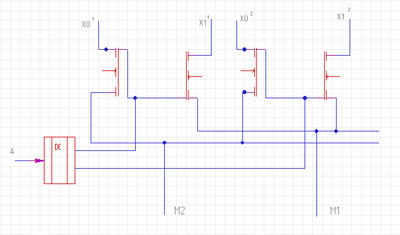

Схема селектора

Рис 1.4 Схема селектора

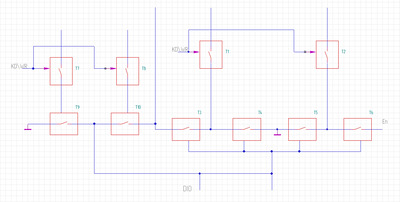

Рис 1.5 Схемы чтения и записи

M0, M1 - шины, которые ведут к узлам A и B (шинам X0, X1).

T10 открыт, когда по M1 приходит "1".

T8 открыт по "0".

"1" только на одной из шин. Если ни один не активен, то на выходе третье состояние.

"0" на входе - 2 средних замкнуты.

T3, T5 - открыты, то DI = "0". Через открытые T1 и T2 - M1 = "1", M0 = "0"

T4, T6 - открыты, то DI = "1". На M0 = "1", M1 = "0"

В случае работы схемы в двунаправленном режиме, "0", "1" подают на них в зависимости от требуемого состояния.

В КМОП-логике получаем самую компактную ячейку памяти (самая предпочтительная).

Для увеличения объёма памяти увеличивают объём кристалла или уменьшают размер элементов.

СОЗУ за счёт своей простоты имеют высокую скорость по чтению/записи. Характеризуются очень высоким энергопотреблением (на триггере постоянно поддерживается питание)

В ТТЛ основная часть энергии тратится на переключение.

Схемы СОЗУ сохраняют состояние благодаря конденсаторам, включённым как фильтры при соединении схем.

Временные диаграммы СОЗУ

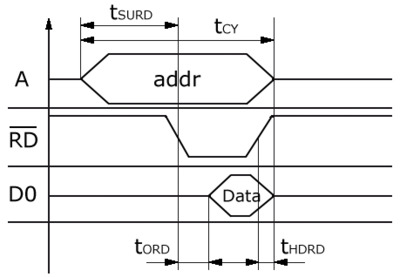

Цикл чтения

Рис 1.6 Временная диаграмма цикла чтения

Время предустановки шины A относительно шины B

tsu(A-B) - интервал времени между началами обоих сигналов.

Время удержания

th(A-B) - интервал времени между началом сигнала A и окончанием сигнала B.

Время сохранения

tr(A-B) - интервал времени между началом сигнала A и окончанием сигнала B.

tSURD - время, через которое подаётся сигнал чтения (его активация реализации)

tORD - время появления данных (относительно времени tSURD)

tHDRD - время удерживания данных при чтении (после снятия сигнала чтения)

Для чтения используются только шины адреса и выхода - они раздельны.

Для чтения на шину адреса подаётся адрес необходимой ячейки. Данные на выходе держатся столько, сколько есть сигнал чтения (асинхронный режим работы).

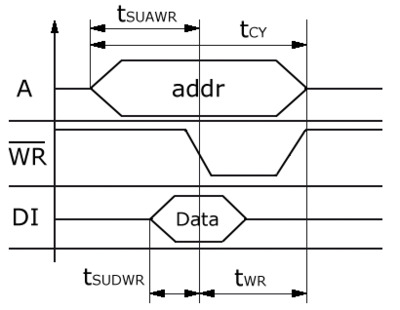

Цикл записи

Рис 1.7 Временная диаграмма цикла записи

Время доступа - импульсное время относительно появления того или иного управляющего сигнала до появления информационного сигнала на выходе.

tWR - в течение этого времени сигнал записи постоянен на выходе

tSUAWR - время, после которого подаётся стробирование записи (есть нормировка стробирования записи!).

При постоянном сигнале записи и адрес и данные должны находиться в том же состоянии, в котором они и были.

При WR = 0 и RD = 0 - режим хранения информации.

Условное обозначение

Рис 1.8 Временные диаграммы. Условные обозначения

Указывает время, в течение которого сигалом является величина, указанная внутри шестиугольника.

Время доступа - время от подачи сигнала на шину адреса до момента получения информации на выходе.

tSURD + tORD - время выборки.

tCY - время цикла - время от момента активации до момента деактивации (когда можно подавать уже другой сигнал на шину адреса) минимально допустимого интервала между последовательными чтениями или записями.

Динамические ОЗУ

Основа

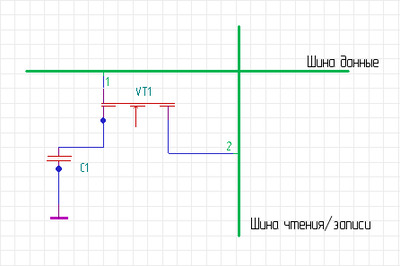

Рис 2.1 ДОЗУ. Базовая ячейка

В качестве базовой ячейки (БЯ) используется конденсатор, при его зарядке хранит заряд, который считать. Для ограничения доступа к нему подключается один транзистор (для подключения к шине данных).

Для дольшего хранения информации конденсатор большей ёмкости (внутренняя ёмкость транзистора единицы пкФ, что не подходит для данных целей).

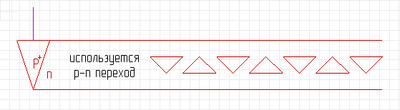

Рис 2.2 Ямочный конденсатор

В результате возник ямочный конденсатор - внутри одного реализован другой. Чем больше их площадь соприкосновения, тем больше ёмкость. В качестве площади - поверхность внутренних граней. Для считывания - верхний электрод.

Время хранения при использовании такого конденсатора порядка 500 нс.

Рис 2.3 Динамические ОЗУ. Общая схема

Основа ДОЗУ - матрица элементов памяти.

Данные хранятся в виде зарядов конденсаторов, образованных элементами МОП-структур. Саморазряд конденсаторов ведёт к разрушению данных, поэтому они должны периодически (раз в несколько мс) регенерироваться. В тоже время плотность упаковки динамических элементов в памяти в несколько раз превышает плотность упаковки, достижимую в статических ОЗУ.

Адресация: шина адреса приходит и на дешифратор и на селектор.

При считывании с конденсатора информация "уходит" ("схема разрушающего считывания").

RAS - "Row Access Select" (strobe)

Адрес на шине адреса - следовательно, RAS = 1. Дешифратор выбирает строку и записывает её в регистр записи. Затем CT и стробирующий сигнал CAS на селектор считывают данные и направляют их на выход.

Для записи значения:

С селектора выбирается вся строка и записывается обратно в матрицу.

Особенности:

- Теперь адрес делится на:

-

- Адрес строки

- Адрес столбца

- Схема дополнена регистром-"защёлкой"

- Схема дополнена двумя стробами (для строки и столбца)

16384 (214) ячеек = 128x128 (27 x 27) Считывание осуществляется построчно

Временные диаграммы

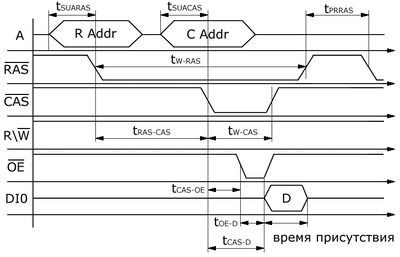

Цикл чтения

Рис 2.4 Временная диаграмма цикла чтения

tPRRAS - время записи содержимого регистра в ЭП матрицы (копирование во внутреннюю схему).

Пока RAS активен копирование строки в регистр, а когда деактивен, данные уходят в ЭП матрицы.

Если RAS активен, то значение строки в регистре, а для перезаписи содержимого регистра в матрицу ЭП требуется tPRRAS.

Время цикла = tCASD.

Время доступа = tSUARAS + tRAS-CAS + tCAS-OE + tOE-D.

При подаче информации: первый адрес строки, длительность сигнала RAS; через какое-нибудь время приходит CAS, т.к за tRAS-CAS выборка строки и запись её в регистр.

tCASD - время выбора селектором и передача данных на выход: от момента перехода от строки к столбцу до момента прихода данных на выходе.

tPRRAS - время восстановления содержимого строки.

Регистр работает в обе стороны (от матрицы элементов памяти и от селектора идут сигналы)

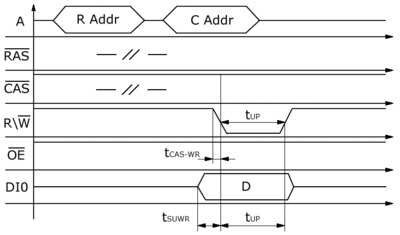

Цикл записи

Рис 2.5 Временная диаграмма цикла записи

tSUWR - время до момента прихода строба записи.

tUP - время удержания записи

tWR так же нормируется

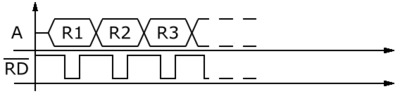

Цикл регенерации

Рис 2.6 Временная диаграмма цикла регенерации

Осуществляется автоматически через 300-500 нс. Работает независимо от WR, RD.

150 нс - время доступа.